# COLLEEN

Ŧ

1

# HARDWARE

# MANUAL

Colleen is the code name for a video game-home computer product that contains a 6502 microprocessor, 4 I/O chips, operating system ROM, and expandable RAM, and several MSI chips for address decoding and data bus buffering.

This manual is intended to primarily describe the 4 I/O chips in sufficent detail to allow experienced programmers to create the operating system code and to create assembly language application ROMS, such as video games. All 4 Input-Output chips are controlled by the microprocessor by writing directly into their registers which are decoded to exist in microprocessor memory space just as RAM does. These I/O chips can also be interogated by the microprocessor by reading simmilar registers.

It is really not necessary for the programmer to know which I/O functions are performed by which of the 4 chips, however it does help in learning these functions.

| CHIP | NAME | FUNCTION |

|------|------|----------|

|      |      |          |

ANTIC

DMA(direct memory access) control. NMI(non maskable interrupt) control. Vertical and Horizontal fine scrolling Light pen position registers Vertical line counter WSYN(wait for horiz. sync)

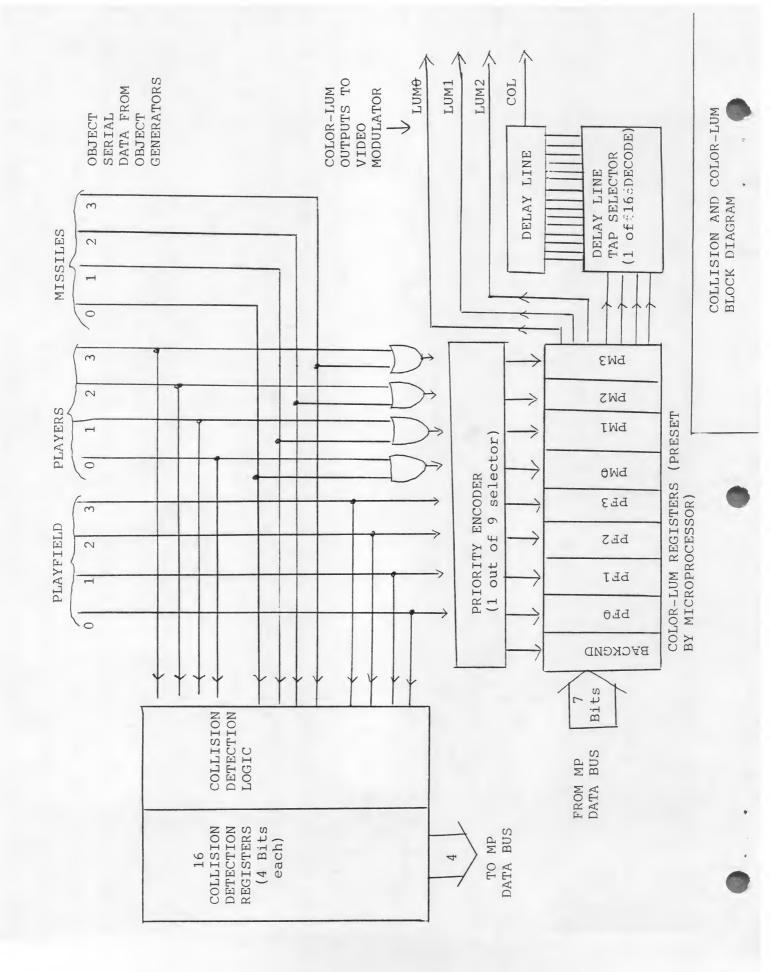

CTIA

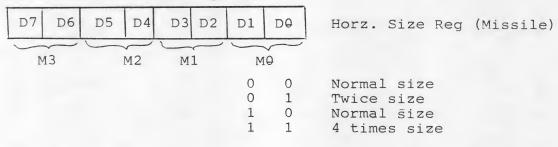

Priority control (display of overlaping objects) Color- Lum control(colors and brightness assigned to all objects including DMA objects from ANTIC) PLAYER-MISSILE objects (4 players & 4 missiles) Graphics registers Size control Horiz. position control Collision detection between all objects Switches and triggers(misc. I/O functions)

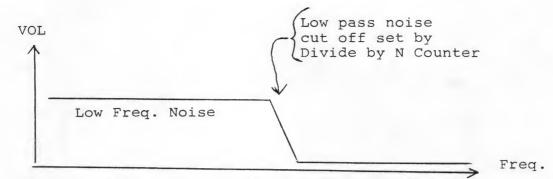

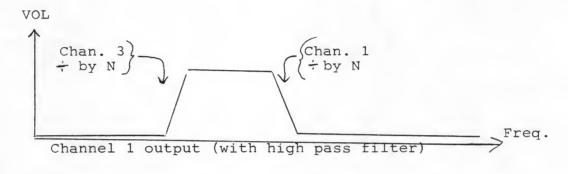

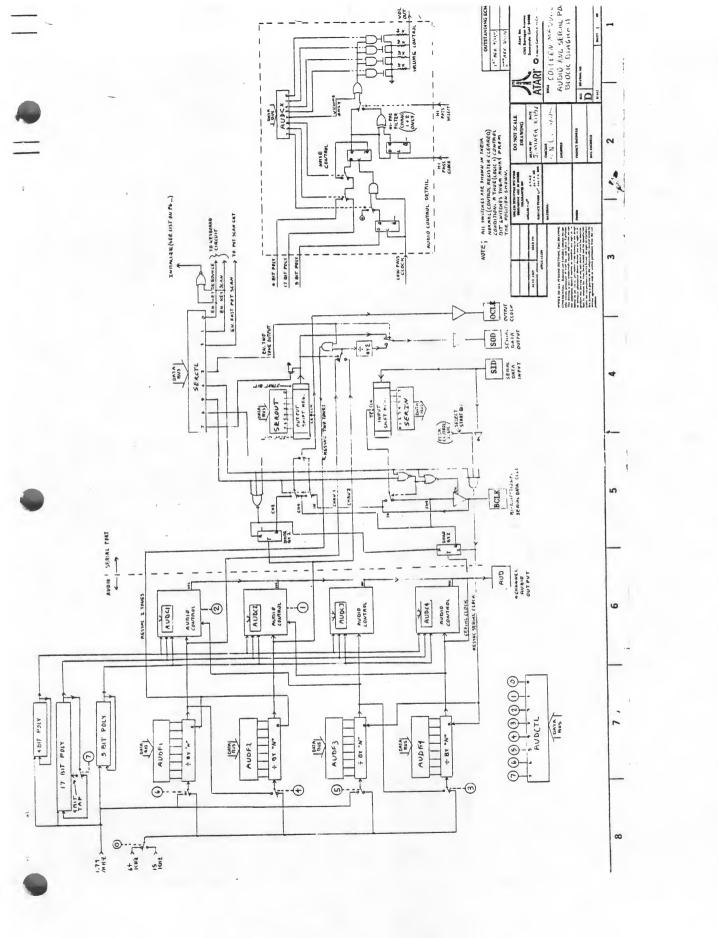

POKEY Keyboard scan and control Serial communications port (bidirectional) Pot scan (digitizes position of 8 independent pots) Audio generation(4 channels) Timers IRQ(maskable interrupt) control Random number generator

PIA Controller(Joy stick) jacks read or write Peripheral control and interrupt lines IRQ( maskable)interupt control from peripherals

The next few pages will introduce some of the concepts needed to understand the Colleen I/O system.

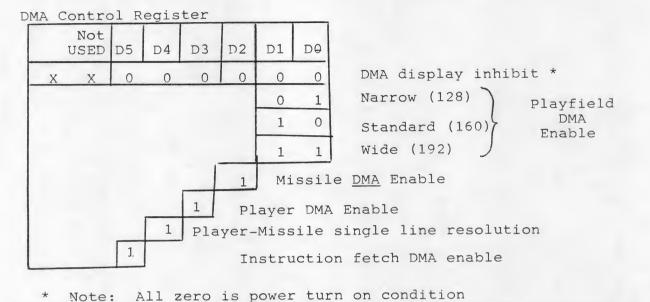

## DMA (Direct Menory Access)

The primary function of the Antic chip is to fetch data from memory (independent of the microprocessor) for display on the TV screen. It does this with a technique called "direct memory access" or DMA. It requests the use of the memory address and data bus by sending a signal called HALT to the microprocessor, causing the processor to become "TRI-STATE"

(open circuit) all during the next computer cycle. The ANTIC chip then takes over the address bus and reads any data it wishes from memory. Another name for this type of DMA is "cycle stealing.

Once initiated, this DMA is completely and automatically controlled by the Antic chip without need for further microprocessor intervention. The DMA control circuit on the Antic chip resembles a small dumb microprocessor. By halting the main microprocessor it can fetch it's own instructions from memory(the display list) addressed by its program counter (display list pointer). Each instruction defines the type (alpha character or memory map), and the resolution(size of bits on the screen), and the location of data in memory, to be displayed on the next group of lines.

In order to begin this DMA the main microprocessor must store a display list of instructions in memory, store data to be displayed in memory, tell the Antic where the display list is(initalize the display list pointer) and enable the DMA control flags on the Antic(DMACTL register).

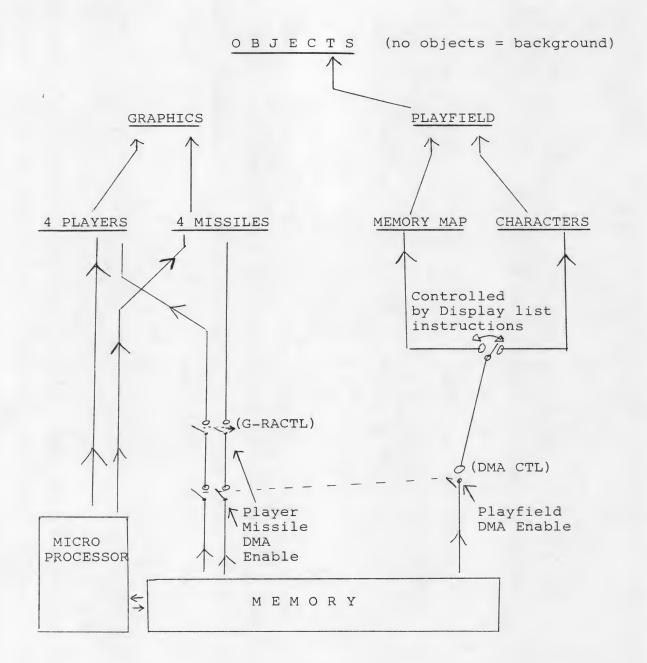

In addition to the type of DMA described above, that is used to generate Alpha Numeric characters and memory map (playfield) displays, the Antic chip simultaniously controls another DMA channel. This type of DMA addresses PLAYER-MISSILE graphics data stored in memory and passes the graphics data on to the CTIA chip graphics registers. This type of DMA (if enabled) occurs automatically interspersed with the playfield DMA described previously. This PLAYER-MISSILE DMA has no display list or instructions, and is therefore much simplier than the PLAYFIELD DMA.

In order to begin PLAYER-MISSILE DMA the main microprocessor simply tells the Antic chip where the data is located in memory (loads the player-missile base register PMBASE) and enables the proper DMA control flags on the Antic chip (DMACTL reg.) and on the CTIA chip (GRACTL reg.).

In addition to the two types of DMA described above, the Antic chip also generates DMA addresses for the refresh of the dynamic memory RAMS used in this system. This is also completly automatic and need be considered by the programmer only if he is concerned with real time programming where an exact count of the computer cycles remaining(after the 3 types of DMA have taken their cycles) is important.

The data fetched by the Antic with PLAYFIELD DMA (Alpha characters or memory map) is stored in a shift register and converted into real time serial output for transmission to the CTIA chip where it is assigned a color-luminance, and compared against other displayed objects for collision detection and priority assignment.

The data addressed by Antic PLAYER-MISSILE DMA(players and missiles) is routed directly to shift registers on the CTIA chip where it is converted into real time serial data representing individual players and missiles, which are assigned color-lum values and compared against each other and Playfield for collision detection and priority assignment.

# OBJECTS

There are basically two types of objects produced by the I/O chips for display on the TV screen ; graphics objects and playfield objects. Area on the screen where there are no objects is called Background. Background is not the same as blank or black. It is simply the area where objects are not.

Graphics objects are further divided into Players and Missiles. They are limited in width to 8 bits for each player and 2 bits for each missile. Their vertical height is unlimited. Their horizontal position on the screen is determined by a horizontal position register for each object. Player-Missile data can be fetched from memory by the microprocessor or by the Antic chip (using Player-Missile DMA). This data is then stored by the microprocessor(or automatically by DMA) in registers on the CTIA chip where it is held and outputted to the TV screen whenever the horizontal sync counter equals one of the horizontal position registers. Players and missiles will appear as vertical bars unless their data registers are changed by the microprocessor(or by the data in memory if in Player Missile DMA) during the actual screen display time.

Playfield objects are further divided into Memory map and Characters. Unlike Player-Missile objects that can be moved by simply changing their horiz.position register, Playfield objects have a location on the screen that is determined by their location in memory, and by parameters stored by the microprocessor in the DMA dispragalist in memory. Memory Map playfield data is fetched from memory automatically by the Antic chip where it is placed in a shift register and converted to serial output for the TV display. Character playfield data, in contrast, requires two fetches from memory by the Antic chip. First the Antic fetches the names of the characters from memory and places them in a shift register. These character names are then used to address the actual data which is fetched from memory and converted to serial output for the TV display. All playfield serial output data passes through the CTIA chip before being sent to the TV display. There it is assigined Color-luminance and Priority and tested for Collisions with Graphics objects

#### COLOR LUM

A color luminance register is used on the CTIA chip for each Player-Missile and Playfield type. Each Color-lum register is loaded by the microprocessor with a code representing the desired color and luminance of it's corresponding Player-Missile or Playfield type. As the serial data passes through the CTIA chip it is "impressed" with the color and luminance values contained in these registers, before being sent to the TV display.

# PRIORITY

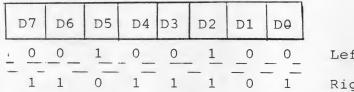

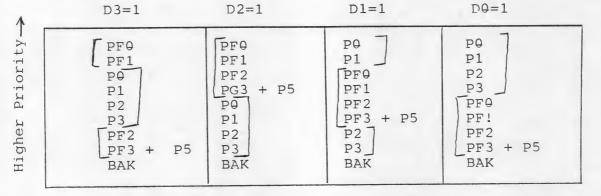

When moving objects such as players and missiles, overlap on the TV screen(with each other or with Playfield)a decision must be made as to which object shows in front of the other. Objects which appear to pass in front of others are said to have Priority over the ones they pass in front of. Priority is assigned to all objects by the CTIA chip before the serial data from each object is combined with the other objects and sent to the TV screen.

The priority of objects can be controlled by the microprocessor by writing into the control register PRIOR. The functions of the bits in this register are given in the table on page B4.

#### COLLISIONS

Overlaping objects are considered to have collided. This is detected by a real time occurance of simultanious serial data from more than one object generator. Hardware register bits are used to store 60 of the possible 72 collisions. These collision bits can be read by the Microprocessor as described on pg.11 and B6.

#### INTERRUPTS

Interrupts are described extensively on pg. 20. Below is a brief list to itemize the types of interrupts provided.

Instruction interrupt. (requested by any display instruction) Vertical Blank int. (req. by beginning of vertical blank) Reset button int. (req. by pushing reset button on panel) Break key int. (req. by pushing break key) Other key int. (req. by pushing any key) Serial input int. (req. by serial port input) Serial output int. (req. by serial port output) Transmission finished int. (req. by serial port output) Timer interrupts (3 each, req. by audio timers)

Peripheral interrupts (2each, req. by serial port devices) Almost all of these interrupt sources can be masked on command of the microprocessor and have status bits which can be interogated and reset by the microprocessor. Even the interrupts defined as "non maskable" (NMI) on the microprocessor have mask bits on the I/O chips which can be set by the microprocessor.

#### ₩SYN

In addition to a Vertical Blank Interupt, which allows the microprocessor to synchronize to the vertical TV display, this system also provides a Wait for Horizontal Sync (WSYN) command that allows the Microprocessor to synchronize itself to the TV horizontal line rate. This sync takes effect when the processor writes to an I/O location called WSYN, whenever it desires horizontal synchronization. Writing to this address sets a latch which pulls to zero a pin on the microprocessor called READY. When READY goes to zero the microprocessor stops and waits. The tatch is automatically reset(returning READY true) at the beginning of the next horizontal blank interval, releasing the microprocessor to resume program execution.

| I SCROLL<br>V SCROLL | X                                                                               | X                 | XY          | <u>X</u>             | X                         | XX   |         | X                                 | X                                        | XX                            | X                 | X         | XX                                       | Horizontal Scrolli<br>Vertical Scrolling | Scrolling<br>rolling |

|----------------------|---------------------------------------------------------------------------------|-------------------|-------------|----------------------|---------------------------|------|---------|-----------------------------------|------------------------------------------|-------------------------------|-------------------|-----------|------------------------------------------|------------------------------------------|----------------------|

| LD MFW SCAN          |                                                                                 |                   | <u>^</u>    | XX                   | X                         | X    |         | 5<br>1<br>2                       | 27-0                                     | $\wedge$                      | X                 | X         | X                                        | Load memory so                           | scan.(3 byte)        |

| INST INTERUFT        |                                                                                 | The second second | Canal Canal | Codebility: di verte |                           | -    | X       | X                                 | X                                        | X                             | X                 | X         | X                                        | Display instru                           | instruction interupt |

| BLK 1                |                                                                                 |                   |             |                      |                           |      | 000     | ui u cartila aurolata             | ula Talandrad Roads                      | 128 44 e A <b>nne an</b> 1979 |                   |           |                                          | Blank 1 line                             |                      |

| . 2                  |                                                                                 |                   |             |                      | mmäsäd guract - ,         |      | 90      | andre in Analysis                 | unanan kuutu                             | tar William Big               |                   |           | aanusto dourto                           | Blank 2 lines                            |                      |

| " 3-7                |                                                                                 |                   |             | was haddhirthid the  | addresses                 |      | 0       | Theory or server.                 | MON-INFO                                 | la datar terih wan di         |                   | WT ( )-17 | etted titel and e<br>definision of the e | Blank 3 thru 7                           | 7 lines              |

| =                    | 0.2                                                                             |                   |             | NAMES OF A COMPANY   | Datus Continent           |      | FO      | March Scillars was af             | CANA DE ASSAULT                          | معاديمون درابرد               |                   |           | 49                                       | Blank 8 lines                            |                      |

| JMP                  |                                                                                 |                   |             |                      | ills we der f. de after V |      | 81      | han y 499 , Badat <sup>3</sup> ). | an a | aan - alata , % aa %          |                   |           | an e 197                                 | Jump (3 byte instruction)                | instruction)         |

| JVB                  | 14<br>14<br>14<br>14<br>14<br>14<br>14<br>14<br>14<br>14<br>14<br>14<br>14<br>1 |                   | VERNINGE    |                      | A HAUDINES                |      | 5       | 62.86°29.5° 844                   | WTHOMAS AND                              | 1986 m (Alton Alton           | -1- <del></del> - |           | an san an                                | Jump & wait fo                           | for vert.Blank       |

| CHR(40,2,8)          | 212                                                                             | 22 3              | 2 4         | 2 52                 | 65                        | 72   | 82      | 92 4                              | A2 E                                     | B2 C2                         | 2 D2              | 24        | F2                                       | (                                        | (Also 3 Byte)        |

| " (40,2,10)          | 01                                                                              | 23 3              | 34          | 3 53                 | 2 63                      | 22   | 83      | 93 1                              | A3 E                                     | B3 C                          | 3 D3              | E3        | E13                                      |                                          |                      |

| " (40,4,8)           | 0.114                                                                           | 24 3              | 4 4         | 4 54                 | 1 64                      | 74   | 84      | 94 1                              | A4 E                                     | B4 C4                         | 4 D4              | E4        | F4                                       |                                          |                      |

| ** (40,4,16)         | 05 15 2                                                                         | 25 3              | 5 4         | 5 55                 | 69 9                      | 52   | 85      | 95 4                              | A5 E                                     | B5 C                          | 5 D5              | ED        | FIS                                      | ) Mode                                   |                      |

| " (20,5,8)           | 16                                                                              | 26 3              | 6 4         | 656                  | 5 66                      | 76   | 86      | 961                               | A6 B                                     | B6 C6                         | 5 D6              | E6        | F6                                       | Instructions                             | 10                   |

| " (20,5,16)          | 07 17 2                                                                         | 27 3              | 14          | 757                  | 1 67                      | 77   | 87      | 1 16                              | A7 E                                     | B7 C7                         | TD7               | EJ        | F7                                       |                                          |                      |

| MAP(40,4,8)          | 03 13 2                                                                         | 28 3              | 38 4        | 85 3                 | 63                        | 78   | 38      | 98 1                              | A8 E                                     | B8 C8                         | 3 D8              | E8        | F8                                       | _                                        |                      |

| и (80,2,4)           | 09 19 2                                                                         | 29 3              | 01<br>01    | 9 59                 | 9 69                      | 79   | 68      | 1 66                              | A9 E                                     | B9 C9                         | 60 C              | E         | F9                                       |                                          |                      |

| H (80,4,4)           | VI FC                                                                           | 2A 3              | A Martin    | A 5A                 | 1 6A                      | TA   | 8A<br>A | 9A 1                              | AAB                                      | BA CA                         | A DA              | EA        | FA                                       |                                          |                      |

| " (160,2,2)          | OB 1B                                                                           | 2B 3              | 384         | B 5B                 | 3 6B                      | 7B   | BB      | 9B                                | ABE                                      | BBCB                          | B DB              | EB        |                                          | Memory Map                               |                      |

| и (160,2,1)          | 01 00                                                                           | 20 3              | 30.4        | C 5C                 | 090                       | 70   | 80      | 106                               | ACE                                      | BCCC                          | DC                | EC        | CF.                                      | Instructions                             | 70                   |

| " (160,4,2)          | 01 1D 2                                                                         | 2D 3              | 3D 4        | D 5D                 | 0 6D                      | 7D   | 3D      | 9D /                              | AD E                                     | BD CD                         | DD                | ED        | Ð                                        |                                          |                      |

| " (160,4,1)          | OE 1E 2                                                                         | 2E 3              | YEY.        | E 5E                 | E 6E                      | 7E   | 8E      | 9E I                              | AEE                                      | BECE                          | E DE              | EE        | FE                                       |                                          |                      |

| H (320,2,1)          | OF 1F' 2                                                                        | E                 | 2F 3F 4F    | F 5F                 | 19 E                      | 7F   | 8F      | H.H.6                             | AFE                                      | BFCF                          | HOH               | EF        | HH                                       |                                          |                      |

| AN N                 | -Ilumber                                                                        |                   | TV<br>Col   | lines<br>ors(Ba      | es p<br>(Bac              | Pr O | cell    |                                   | lay                                      | + Playfield                   | 73                | types     |                                          |                                          |                      |

|                      | T                                                                               | 9                 | 7.7         |                      | · · ·                     |      |         | -                                 | 1+r r+0/                                 | 1111                          |                   |           | -                                        |                                          |                      |

·...

I4.5

0 υ Ч 0 N 0 н E υ D К H S N Н  $\succ$ A Г Д S

DI

DES

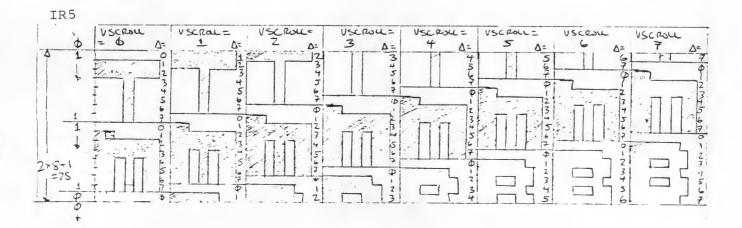

# VERTICAL AND HORIZONTAL FINE SCROLLING

Playfield objects are difficult to move smoothly. Memory map playfield can be moved by rewriting sections of memory, however this is extremely time consuming if large sections of the screen must be moved smoothly. Character playfield objects can be moved easily in a jerkey fasion by changing the memory scan counter, however this results in a large position jump from one character position to another, not a smooth motion. For this reason hardware registers and counters are provided to allow smooth horizontal or vertical motion, up to one character width horizontally and up to one character height vertically. After this much smooth motion has been done by increasing the value in these registers, memory is rewritten or the memory scan counter is modified and smooth motion is resumed for another character distance. The details of the use of these registers is given on pg.12 and pg.A4

### LIGHT PEN

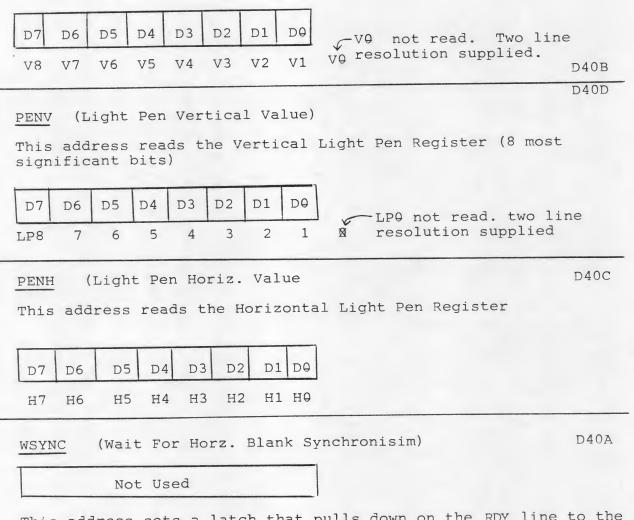

A "light pen" input is provided which is connected to the Antic chip. This light pen signal captures the value of the vertical line counter and the horizontal sync counter in two registers, PENV and PENH, whenever the signal goes from true to false because of light falling on the light pen. The microprocessor can then read these two registers to determine the pen vertical and horizontal position.

### VERTICAL LINE COUNT

The microprocessor can also read a location that contains the present TV line number being displayed. This allows the microprocessor to modify the display depending on the present vertical location of the TV spot creating the display.

#### OBJECT GENERATION

Objects can be generated either as playfield or as playermissile graphics. (see pg 2) These are two distinct, almost independent, object generating circuits.

# PLAYER-MISSILE GRAPHICS GENERATION

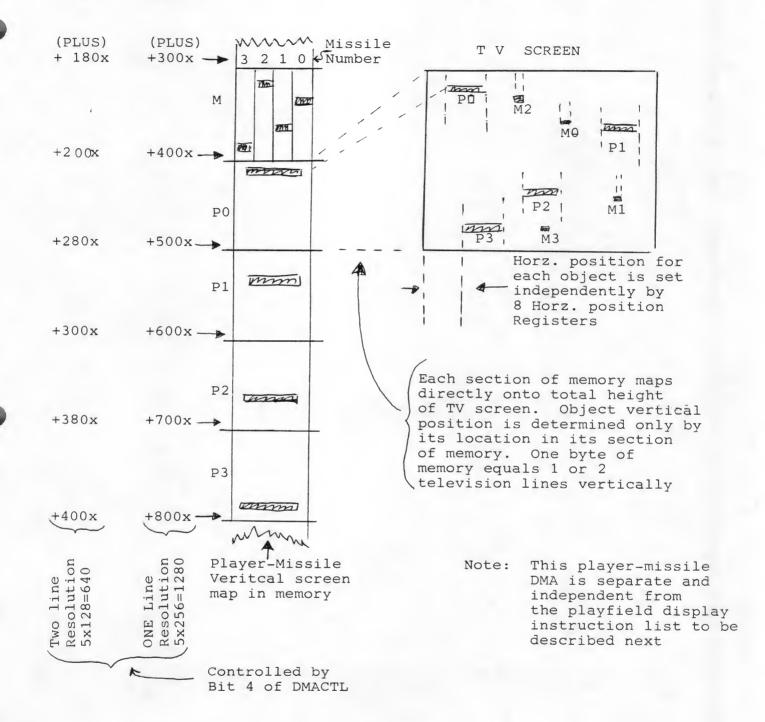

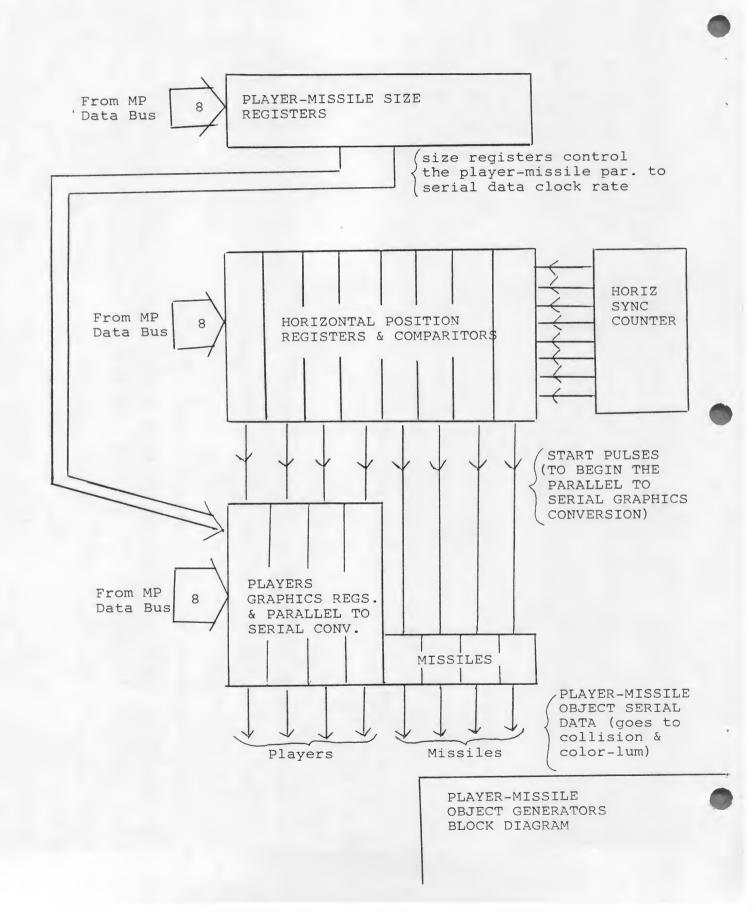

There are 8 graphic objects, 4 players and 4 missiles, the 4 missiles may be grouped together and used as a 5th player, these objects are positioned horizontally by 8 horz. position registers. (HPOS (X)). These registers may be reloaded at any time by the processor, allowing an object to be replicated many times across a horizontal TV line.

The shape of a player-missile, is determined by the data in its graphics register (GRAF(X)). Players have independent 8 bit graphic registers. The four missiles have 2 bit registers (located within one address). These registers may also be reloaded at any time by the processor, although they are usually changed during horizontal blank time. The data in each graphics register is placed on the display whenever the horizontal sync counter equals the corresponding horizontal position register. The same data will be displayed every line unless the graphic registers are reloaded with new data.

The player-missile graphic registers may be reloaded by the microprocessor (GRAF(X)), or automatically directly from memory with direct memory access (DMA). The programmer must place the object graphics in memory, (see pg 3). write the player-missile base address (PMBASE), and enable player-missile DMA (DMACTL, GRACTL). The transfer of object graphics from memory to display is then fully automatic.

#### PLAYFIELD GENERATION

Playfield is always generated by DMA. There are 4 types of playfield, each identified by its own color-lum register and collision detection. Playfield is generated by two different DMA techniques; memory map and character. Both methods provide list of instructions in memory, independent of the player-missile generation.

# OBJECT DISPLAY SOURCES

2

Player-Missile Base Address (PMBASE) Nx1024 Nx2048

PLAYER-MISSILE DMA

3

## PLAYFIELD DMA

## Display List

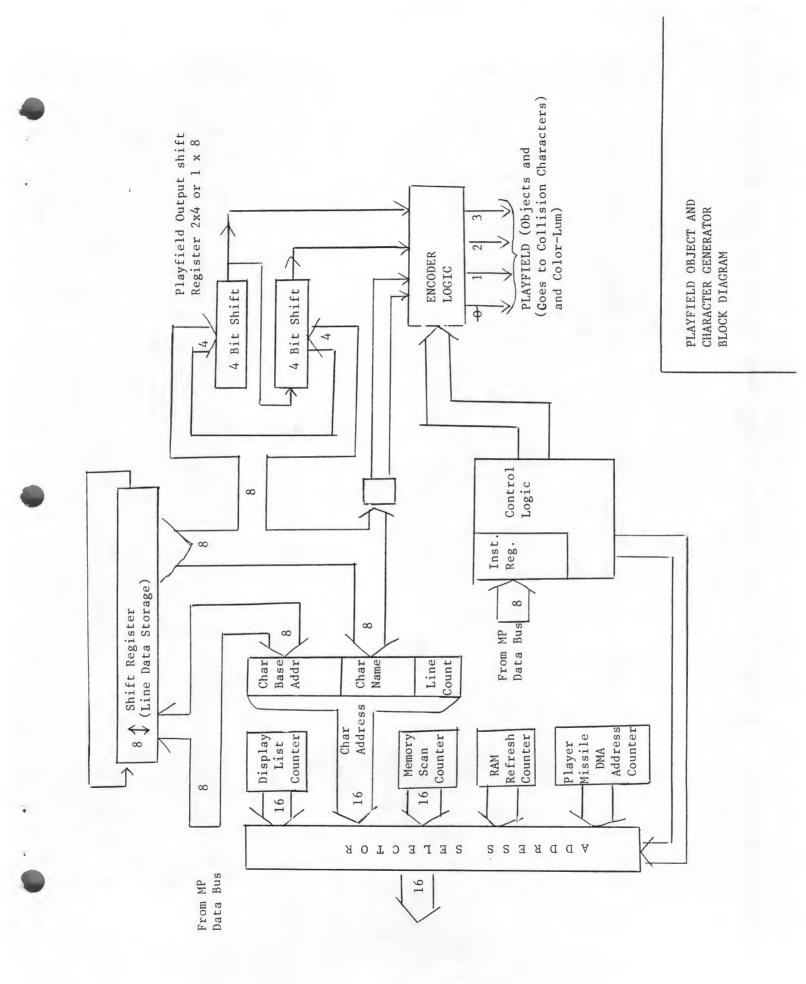

The display list is a sequence of display instructions stored in memory. These instructions are either one Byte, or 3 Bytes long. The display list can be considered a display program, and the <u>Display List Counter</u> that fetches these instructions can be thought of as a display program counter. (10 bit counter plus 6 bit base reg.)

The display list counter can be initalized at any time by writing to DLISTH and DLISTL. Once initalized this counter value is used to address the display list, fetch the instruction, display 1 to 16 lines of data on the TV screen, increment the display list counter, fetch the next display instruction, and so on automatically without microprocessor control. (see pg Al for dlist bits)

Each instruction defines the type (alpha character or memory map) and the resolution (size of bits on screen) and the location of data in memory to be displayed, for a group (1 to 16) of lines. Each group of lines is called a display block.

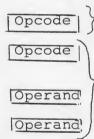

## DISPLAY INSTRUCTION FORMAT

Each intruction consists of either an Opcode only, or of an Opcode followed by 2 Bytes of operand.

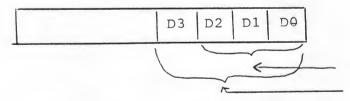

Sincle Byte Display Instruction

Triple Byte Display Instruction

The Opcode is always fetched first and placed in the <u>Instruction</u> <u>Register</u>. This Opcode defines the type of instruction (one or three Byte) and will cause two more bytes to be fetched if needed. If fetched, these next 2 bytes will be placed in the <u>Memory Scan Counter</u>, or in the <u>Display List Counter</u> (if instruction is a Jump).

## DISPLAY INSTRUCTION REGISTER

This register is not directly accessable by the programmer. It is loaded with the Opcode of each instruction.

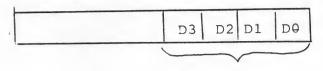

| D7 | D6 | D5 | D4 | D3 | D2  | D1 | D0 |

|----|----|----|----|----|-----|----|----|

| Х  | 0  | 0  | 0  | 0  | 0   | 0  | 0  |

| Х  | 0  | 0  | 1  | 0  | 0   | 0  | 0  |

| x  | 1  | 1  | 1  | 0  | 0   | 0  | 0  |

| 0  | х  | х  | x  | x  | x   | x  | х  |

| 1  | x  | х  | x  | х  | x : | x  | x  |

| x  | 0  | x  | x  | 0  | 0   | 0  | 1  |

| x  | 1  | x  | x  | 0  | 0   | 0  | 1  |

| Blank 1 line )  | Actually   |

|-----------------|------------|

| Blank 2 lines   | Background |

| Blank 2 lines > | color-lum  |

| Blank 8 lines / | not black. |

No Interrupt

Interrupt (bit 7 of NMI status)

## Jump

Jump and wait (no display) until end of next vertical blank time. (Jumps are 3 bytes and they reload display list counter)

### No Interrupt

Interrupt(bit 7 of NMI Statue)

One Byte Inst. 3 Byte inst. (Reload Mem. Scan Counter) No Vertical Scroll Vertical Scroll No Horizontal Scroll Horizontal Scroll

Display Mode Opcodes (Jump & Blank Excluded) See list of Display Modes on pg. 7 10 & 11

#### MEMORY SCAN COUNTER

0

1

x

x

0

1

x

X

x

x

0

1

x

X

x

x

x

х

0

1

х

x

x

х

$\mathbf{x}$

х

x

X

x

X

x

x

x

х

x

x

x

x

x

X

х

х

х

X

x

x

х

x

х

x

х

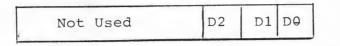

This counter is not directly accessable by the programmer. It is loaded with the value in the last 2 Bytes of a 3 Byte (non Jump) instruction.

This counter points to the location (address) in memory of data to be directly displayed (memory map display) or to the location of character name strings to be indirectly displayed (character display).

A single Byte instruction does not reload this counter. This implies a continuation in memory of data to be displayed from that displayed by the previous instruction. Since this counter really Consists of 4 bits of register and 12 bits of actual counter, a continuous memory block cannot cross 4K Byte memory boundaries, unless the counter is repositioned with a 3 byte type of instruction. (Non Jump 3 byte instruction)

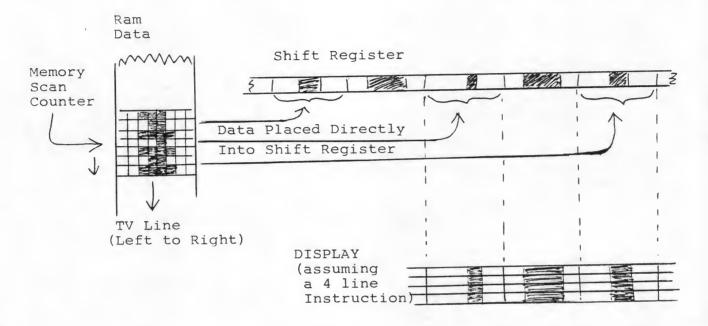

## MEMORY MAP DISPLAYS

Display data is fetched directly by the memory scan counter and placed in a shift register. This shift register is used to display as many lines as required by the display instruction.

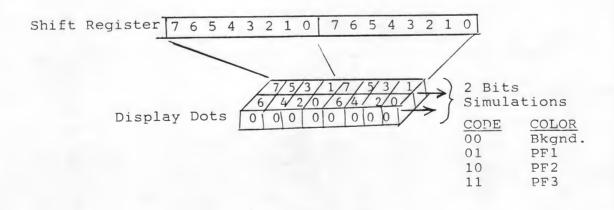

Some instructions compress data in the shift register to give a two bit deep display. The two bits of depth allow each display dat to be identified as background (Both Bits Zero) or as one of 3 types of playfield.

6

## MEMORY MAP DISPLAY INSTRUCTIONS

Data in memory (addressed by the memory scan counter) is displayed directly, when executing a memory map display instruction. As data is being displayed it is also stored in a shift register so that it can be redisplayed for a many TV lines as required by the instruction.

| Basic | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | -(Instruction Register Bits)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Std.<br>Horiz<br>Bits | Color                                                 | 1     |      |

|-------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------------------------------------|-------|------|

| mode  | 3210                                    | Output Displayed by each Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Displ                 | Lum                                                   | Lines | Data |

| 8     | 1 1 1 1                                 | $\frac{7/6/5/4/3/2/10}{1} \downarrow 1 \text{ lobs-} \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \uparrow \\ 1 \text{ TV Line} \\ 1 \text{ TV Line} \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \uparrow \\ 1 \text{ TV Line} \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \uparrow \\ 1 \text{ TV Line} \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \uparrow \\ 1 \text{ TV Line} \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \uparrow \\ 1 \text{ TV Line} \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \uparrow \\ 1 \text{ TV Line} \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \uparrow \\ 1 \text{ TV Line} \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \uparrow \\ 1 \text{ TV Line} \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \uparrow \\ 1 \text{ TV Line} \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \uparrow \\ 1 \text{ TV Line} \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \uparrow \\ 1 \text{ TV Line} \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \uparrow \\ 1 \text{ TV Line} \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \uparrow \\ 1 \text{ TV Line} \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \uparrow \\ 1 \text{ TV Line} \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \uparrow \\ 1 \text{ TV Line} \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \uparrow \\ 1 \text{ TV Line} \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \uparrow \\ 1 \text{ TV Line} \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \uparrow \\ 1 \text{ TV Line} \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \downarrow \\ 1 \text{ TV Line} \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \downarrow \\ 1 \text{ TV Line} \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \downarrow \\ 1 \text{ TV Line} \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \downarrow \\ 1 \text{ TV Line } \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \downarrow \\ 1 \text{ TV Line } \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \downarrow \\ 1 \text{ Clock } \rightarrow   \not\leftarrow \downarrow \\ 1 \text{ TV Line } \\ \frac{1}{2} \text{ Clock } \rightarrow   \not\leftarrow \downarrow \\ 1 \text{ Clock } \rightarrow   \not\leftarrow \downarrow \end{matrix}$ | 320                   | PF2 Ø<br>PF1 1<br>(Lum<br>only)                       | 1     |      |

| -     | 1 1 1 0                                 | 1 Clock $\uparrow$ 1 TV Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 160                   | BK PF1 /<br>PF2 2<br>PF3 3                            | 1     |      |

| 7     | 1 1 0 1                                 | 1 Clock 72 TV Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 160                   | BK Ø<br>PFO I<br>PF1 <sup>2</sup><br>PF2 <sup>3</sup> | 2     | •    |

| -     | 1 1 0 0                                 | 1  Clock   = 1  TV Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 160                   | BK<br>PF0                                             | 1 .   |      |

| 6     | 1 0 1 1                                 | 1 Clock     2 TV Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 160                   | BK Ø<br>PFØ 1                                         | 2     |      |

| 5     | 1010                                    | 2 Clocks   F 1/4 TV Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 80                    | BK Ø<br>PFO 1<br>PF1 2<br>PF2 3                       | 4     |      |

| 4     | 1001                                    | 2 Clocks   < 4 TV Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 80                    | BK Ø<br>PFQ J                                         | 4     |      |

| 3     | 1000                                    | 4 Clocks 18 TV Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 40                    | BK ¢<br>PF0 1<br>PF1 2<br>PF2 3                       | 8     |      |

|       | Note:                                   | All memory map and character instruct<br>display data as one of 4 types of pla                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ions -<br>ayfield     | or                                                    | l     | 0    |

display data as one of 4 types of playfield or background, each with it's own separate color-lum register. 7

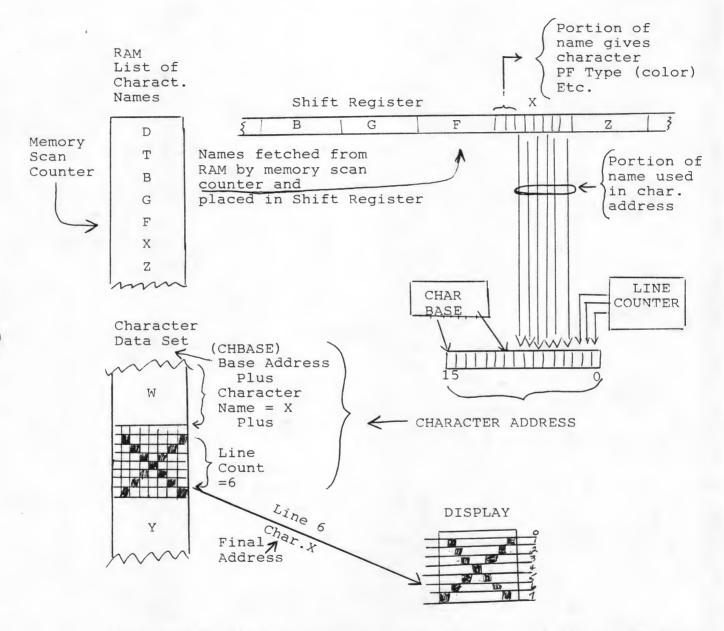

#### CHARACTER DISPLAYS

Character names (codes) are fetched by the memory scan counter, and are placed in a shift register. On any given line of display, the shift register rotates changing only the name portion of the character address. as shown below.

After a full line of character data has been displayed the  $\triangle$  line counter increments. The next line again addresses all characters by name for that  $\triangle$  line number.

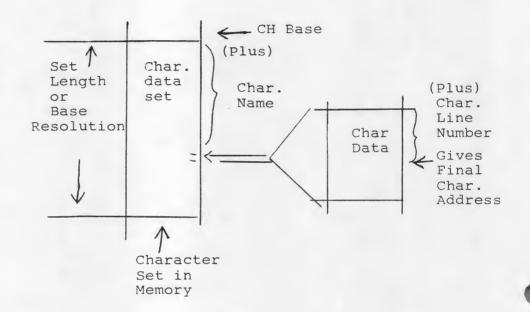

Only the most significant 6 or 7 bits of the character base register are used in the final address, depending on the instruction type. Character sets therefore come in 2 different sizes; 512, and 1024 Total Bytes (Max).

| Char.<br>Instruc<br>Code | Char.<br>Display<br>Type | Set<br>Length<br>Base Reso<br>Iution | Number<br>of Char.<br>in set | Bytes<br>Per<br>char. |

|--------------------------|--------------------------|--------------------------------------|------------------------------|-----------------------|

| 011X                     | 20x5                     | 512<br>Bytes                         | 64                           | 8                     |

| 010X                     | 40x4                     | 1024<br>Bytes                        | 128                          | 8                     |

| 001X                     | 40x2                     | 1024<br>Bytes                        | 128                          | 8                     |

| Character.<br>per une    | s #of col                | L Base                               | = N x Blo                    | ck Lengtl             |

Different portions of the character name are used in the final address, also depending on the instruction type as shown in the following list of character instructions.

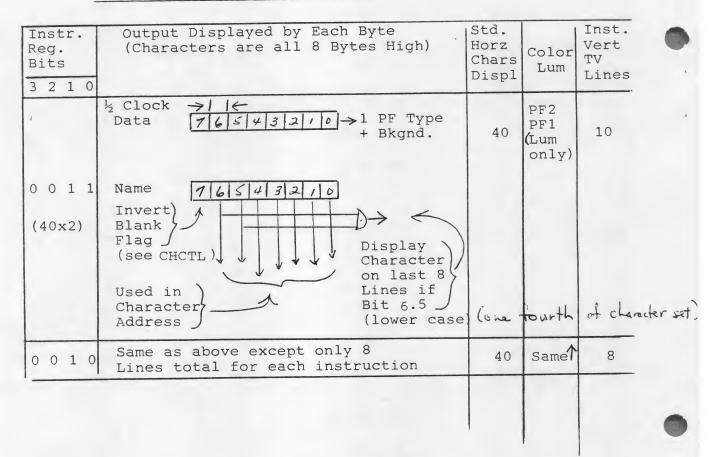

#### CHARACTER DISPLAY INSTRUCTIONS

Data in memory (addressed by the memory scan counter) is not displayed directly when executing a character display instruction. The memory scan counter points instead to a list of character names. This list of names might for example contain the ASCII code names for alpha-numeric characters to be displayed. This name list is fetched by the memory scan counter and placed in a shift register. These character names are then combined with the TV line count, and the character base address, to create the <u>character address</u>. That actually fetches character data to be displayed. (see "CHBASE" pg. D40F)

| IR BITS           | Output Displayed by each Byte<br>(All Characters are 8 Bytes High)                                                                      | Std<br>Horz<br>Char<br>Disp | Color<br>lum                                                                              | Inst.<br>Vert.<br>TV<br>Lines | data= X      |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------|-------------------------------|--------------|

| 0 1 1 1<br>(20x5) | 1 Clock $1 \neq 2$<br>Data 76543210 $\rightarrow$ Background<br>(Four PF)<br>Codes<br>Name 76543210<br>(Used in<br>Character<br>Address | 20                          | BK <b>#</b><br>PF9 <b>\$</b><br>PF1 <i>i</i><br>PF2 <b>2</b><br><u>PF3</u> <b>3</b><br>=5 | 16                            | Nane<br>Bits |

| 0 1 1 0           | Same as above except each data<br>Byte shown for 1 line instead of 2                                                                    | 20                          | same                                                                                      | 8                             |              |

| 0 1 0 1<br>(40x4) | 1 Clock<br>Data<br>Name 7 6 5 4 3 2 1 0<br>Used in Char. Add.                                                                           | [11=<br>if<br>or            | BK $\circ$<br>PF0 1<br>PF1 2<br>PF2 3<br>=4<br>PF3<br>CH 7=<br>PF2<br>bit 7 of            | 16<br>]<br>name=Ø             |              |

| 0 1 0 0           | Same as above except each data<br>Byte shown for 1 line instead of 2                                                                    | 40                          | Same                                                                                      | 8                             |              |

# Character Display Instructions

## HARDWARE COLLISION DETECTION

60 bits of collision register are provided to detect and store overlap (hits) between players, missiles and playfield. These collisions can be read by the microprocessor from addresses D000 through D00F.

16 bits for Missile to Playfield

16 bits for Player to Playfield

16 bits for Missile to Playfield

12 bits for Player to Player (P0 to P0 always reads as zero. ETC.)

The  $\frac{1}{2}$  clock memory map mode (IR code 1111) and the  $\frac{1}{2}$  clock Character mode (IR codes 0011 and 0010) are both playfield type 2 and collisions will be stored in bit 2 of the playfield collision registers.

### VERTICAL SCROLLING, DETAILS OF OPERATION